库利-图基快速傅里叶变换算法(英語:Cooley–Tukey FFT algorithm)[1]是最常見的快速傅里葉變換算法。這一方法以分治法為策略遞歸地將長度為N = N1N2的DFT分解為長度分別為N1和N2的兩個較短序列的DFT,以及與旋轉因子的複數乘法。這種方法以及FFT的基本思路在1965年詹姆斯·庫利和約翰·圖基合作發表《An algorithm for the machine calculation of complex Fourier series》之後開始為人所知。但後來發現,實際上這兩位作者只是重新發明了高斯在1805年就已經提出的算法(此算法在歷史上數次以各種形式被再次提出)。

库利-图基算法最有名的應用,是將序列長為N的DFT分割為兩個長為N/2的子序列的DFT,因此這一應用只適用於序列長度為2的冪的DFT計算,即基2-FFT。實際上,如同高斯和库利與图基都指出的那樣,库利-图基算法也可以用於序列長度N為任意因數分解形式的DFT,即混合基FFT,而且還可以應用於其他諸如分裂基FFT等變種。儘管库利-图基算法的基本思路是採用遞歸的方法進行計算,大多數傳統的算法實現都將顯示的遞歸算法改寫為非遞歸的形式。另外,因為库利-图基算法是將DFT分解為較小長度的多個DFT,因此它可以同任一種其他的DFT算法聯合使用。

離散傅立葉變換的複雜度為 (可參考大O符號)

(可參考大O符號)

快速傅立葉變換的複雜度為 ,分析可見下方架構圖部分,級數為

,分析可見下方架構圖部分,級數為 而每一級的複雜度為

而每一級的複雜度為 ,故複雜度為

,故複雜度為

在FFT演算法中,針對輸入做不同方式的分組會造成輸出順序上的不同。如果我們使用時域抽取(Decimation-in-time),那麼輸入的順序將會是位元反轉排列(bit-reversed order),輸出將會依序排列。但若我們採取的是頻域抽取(Decimation-in-frequency),那麼輸出與輸出順序的情況將會完全相反,變為依序排列的輸入與位元反轉排列的輸出。

我們可以將DFT公式中的項目在時域上重新分組,這樣就叫做時域抽取(Decimation-in-time),在這裡 將會被代換為旋轉因子(twiddle factor)

將會被代換為旋轉因子(twiddle factor) 。

。

![{\displaystyle X[k]=\sum _{n=0}^{N-1}x[n]e^{-j(2\pi {\frac {nk}{N}})}\qquad k=0,1,\ldots ,N-1}](https://wikimedia.org/api/rest_v1/media/math/render/svg/8c1bc58d53eca4db8e882d962288d85cdeca7b9e)

![{\displaystyle =\sum _{n\ even}x[n]W_{N}^{nk}+\sum _{n\ odd}x[n]W_{N}^{nk}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/fd189ceb0840b111ad6650a8f3c346005800e4b2)

![{\displaystyle =\sum _{r=0}^{(N/2)-1}x[2r]W_{N}^{2rk}+\sum _{r=0}^{(N/2)-1}x[2r+1]W_{N}^{(2r+1)k}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/d07a0c81f453e445996a3e0435257d6e8798d447)

![{\displaystyle =\sum _{r=0}^{(N/2)-1}x[2r]W_{N}^{2rk}+W_{N}^{k}\sum _{r=0}^{(N/2)-1}x[2r+1]W_{N}^{2rk}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/03b58a209e5dc96cacbe5427d112edfa4b6b404e)

![{\displaystyle =\sum _{r=0}^{(N/2)-1}x[2r]W_{N/2}^{rk}+W_{N}^{k}\sum _{r=0}^{(N/2)-1}x[2r+1]W_{N/2}^{rk}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/fd254ec25ac6c8b112c96dec2a91b1445fa53257)

![{\displaystyle =G[k]+W_{N}^{k}H[k]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/53bf0cddeac84818155040de470b85dffe948b4e)

在這邊我們要注意的是,我們所替換的G[k]與H[k]具有週期性:

![{\displaystyle {\begin{cases}G[k+{\frac {N}{2}}]=G[k]\\H[k+{\frac {N}{2}}]=H[k]\end{cases}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/00ecf779771f585dedf8e3c907e09ebd2f202592)

还注意到系数具有对称性:

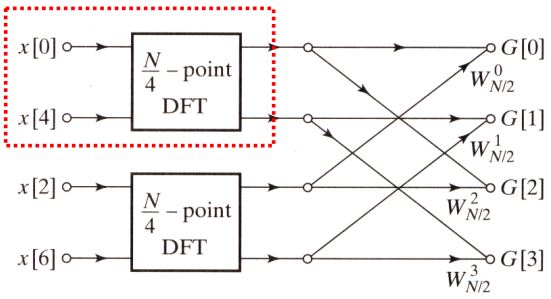

上述的推導可以劃成下面的圖:

劃紅框處所示的 點DFT架構如下圖所示:

點DFT架構如下圖所示:

劃紅框處所示的 點DFT架構如下圖所示:

點DFT架構如下圖所示:

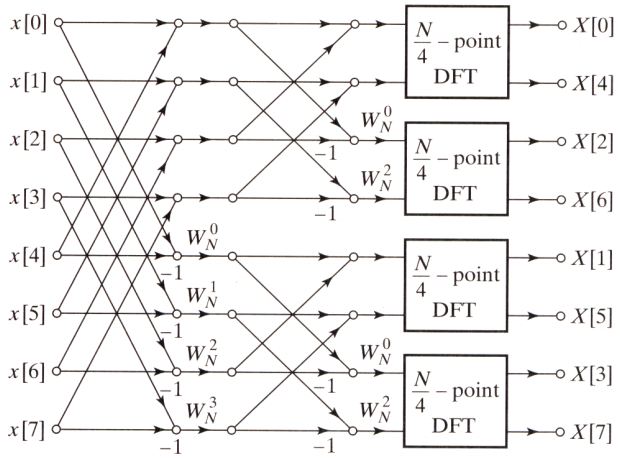

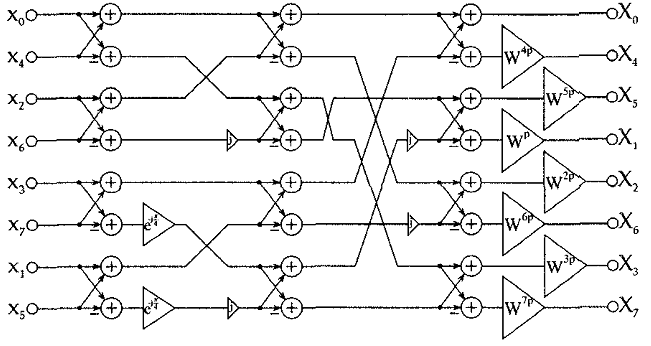

下圖是一個8點DIT FFT的完整架構圖。

我們可以將DFT公式中的項目在頻域上重新分組,這樣就叫做頻域抽取(Decimation-in-frequency)。

首先先觀察在頻域上偶數項的部分:

![{\displaystyle X[2r]=\sum _{n=0}^{N-1}x[n]W_{N}^{n(2r)}\ r=0,1,\cdots ,{\frac {N}{2}}-1}](https://wikimedia.org/api/rest_v1/media/math/render/svg/d2e7461d1b092e029a7bb2af92dccdfd431f7da0)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}x[n]W_{N}^{2nr}+\sum _{n={\frac {N}{2}}}^{N-1}x[n]W_{N}^{2nr}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/801a6470581d07a5f484bbd4b0434f59e32e934e)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}x[n]W_{N}^{2nr}+\sum _{n=0}^{{\frac {N}{2}}-1}x[n+{\frac {N}{2}}]W_{N}^{2r[n+{\frac {N}{2}}]}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/ec893531fefe43082191e7997d6485e87d2b69b0)

![{\displaystyle {\color {Gray}\because W_{N}^{2r[n+{\frac {N}{2}}]}=W_{N}^{2rn}W_{N}^{rN}=W_{N}^{2rn}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/7dad33e79d93241676845acd8cc89b3ff7e5805e)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}x[n]W_{N}^{2rn}+\sum _{n=0}^{{\frac {N}{2}}-1}x[n+{\frac {N}{2}}]W_{N}^{2rn}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/cd9f6e7fcb74256acbca841551e919ef0dbe57d6)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}(x[n]+x[n+{\frac {N}{2}}])W_{\frac {N}{2}}^{rn}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/630f613aad2e2c1cff0a9feea68373e9f0bcda75)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}g[n]W_{\frac {N}{2}}^{rn}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/a0a497711c3349d02cf3fed19e31284de68f4e85)

再觀察在頻域上奇數項的部分:

![{\displaystyle X[2r+1]=\sum _{n=0}^{N-1}x[n]W_{N}^{n(2r+1)}\ r=0,1,\cdots ,{\frac {N}{2}}-1}](https://wikimedia.org/api/rest_v1/media/math/render/svg/2e846f60e833bf7b4c9c564eaf91833c7c4df8df)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}x[n]W_{N}^{n(2r+1)}+\sum _{n={\frac {N}{2}}}^{N-1}x[n]W_{N}^{n(2r+1)}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/f3bec22826122b8c8b86ddc2c63a48c9b05f77e8)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}x[n]W_{N}^{n(2r+1)}+\sum _{n=0}^{{\frac {N}{2}}-1}x[n+{\frac {N}{2}}]W_{N}^{(2r+1)[n+{\frac {N}{2}}]}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/0ba17694e21aaba1b37bf209160d83891c396b1e)

![{\displaystyle {\color {Gray}\because W_{N}^{(2r+1)[n+{\frac {N}{2}}]}=W_{N}^{(2r+1)n}W_{N}^{(2r+1){\frac {N}{2}}}=-W_{N}^{(2r+1)n}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/4d8bb52435fc07264d500482ffec6598856023eb)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}x[n]W_{N}^{(2r+1)n}-\sum _{n=0}^{{\frac {N}{2}}-1}x[n+{\frac {N}{2}}]W_{N}^{(2r+1)n}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/0fbc417eb823a092b4678647586ba94b939ba563)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}(x[n]-x[n+{\frac {N}{2}}])W_{N}^{n(2r+1)}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/b71d627069159f2180bdfc93c021c0a043fdca0b)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}(x[n]-x[n+{\frac {N}{2}}])W_{N}^{n}W_{\frac {N}{2}}^{nr}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/ddaa565a4815dbd7599bc1cad89e8cb86690d0cc)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}(h[n]W_{N}^{n})W_{\frac {N}{2}}^{rn}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/5a60b843e1adbb6c6ad5bc9dcdd3bbaf4d98f6f5)

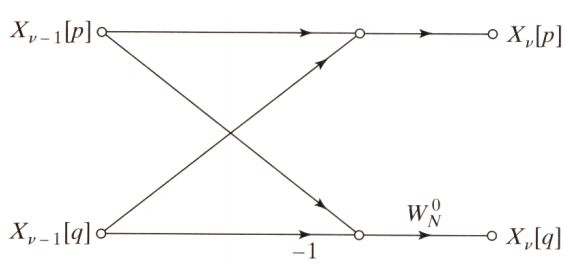

上述的推導可以畫成下面的圖:

更進一步的拆解 -point DFT的架構

-point DFT的架構

下圖為8點FFT下 -point DFT的架構

-point DFT的架構

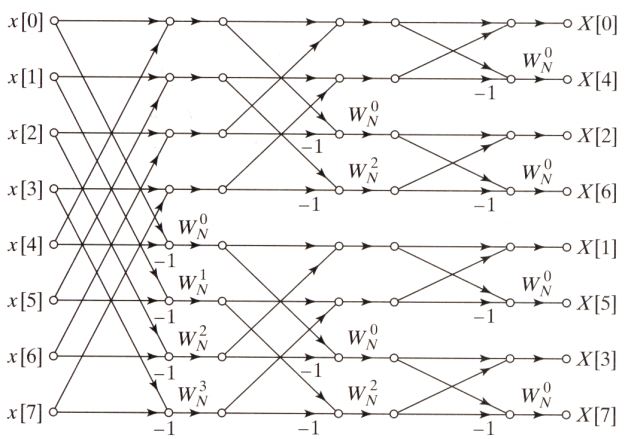

總結上述架構,完整的8點DIF FFT架構圖為

利用库利-图基演算法進行離散傅立葉拆解時,能夠依需求而以2, 4, 8…等2的冪次方為單位進行拆解,不同的拆解方法會產生不同層數快速傅里葉變換的架構,基底越大則層數越少,複數乘法器也越少,但是每級的蝴蝶形架構則會越複雜,因此常見的架構為2基底、4基底與8基底這三種設計。

2基底-快速傅立葉演算法(Radix-2 FFT)是最廣為人知的一種库利-图基快速傅立葉演算法分支。此方法不斷地將N點的FFT拆解成兩個'N/2'點的FFT,利用旋轉因子 的對稱性藉此來降低DFT的計算複雜度,達到加速的功效。

的對稱性藉此來降低DFT的計算複雜度,達到加速的功效。

而其實前述有關時域抽取或是頻域抽取的方法介紹,即為2基底的快速傅立葉轉換法。以下展示其他種2基底快速傅立葉演算法的連線方法,此種不規則的連線方法可以讓輸出與輸入都為循序排列,但是連線的複雜度卻大大的增加。

4基底快速傅立葉變換演算法則是承接2基底的概念,在此裡用時域抽取的技巧,將原本的DFT公式拆解為四個一組的形式:

![{\displaystyle X[k]=\sum _{n=0}^{N-1}x[n]e^{-j(2\pi {\frac {nk}{N}})}\qquad k=0,1,\ldots ,N-1}](https://wikimedia.org/api/rest_v1/media/math/render/svg/8c1bc58d53eca4db8e882d962288d85cdeca7b9e)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{4}}-1}x[4n+0]W_{N}^{(4n+0)k}+\sum _{n=0}^{{\frac {N}{4}}-1}x[4n+1]W_{N}^{(4n+1)k}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/13719c6b6c1cb7e06dab16b2e0e0fbfa4f592a2c)

![{\displaystyle +\sum _{n=0}^{{\frac {N}{4}}-1}x[4n+2]W_{N}^{(4n+2)k}+\sum _{n=0}^{{\frac {N}{4}}-1}x[4n+3]W_{N}^{(4n+3)k}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/a3a0f9401cc8ea8aa63fe510967aa6d40e2bd46c)

![{\displaystyle =W_{N}^{0}\sum _{n=0}^{{\frac {N}{4}}-1}x[4n+0]W_{\frac {N}{4}}^{nk}+W_{N}^{1k}\sum _{n=0}^{{\frac {N}{4}}-1}x[4n+1]W_{\frac {N}{4}}^{nk}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/519a556d3e2ef2460c4166d30864065b29220d11)

![{\displaystyle +W_{N}^{2k}\sum _{n=0}^{{\frac {N}{4}}-1}x[4n+2]W_{\frac {N}{4}}^{nk}+W_{N}^{3k}\sum _{n=0}^{{\frac {N}{4}}-1}x[4n+3]W_{\frac {N}{4}}^{nk}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/cbd2e5ec944fe84a6edf79ef26b9ea82436a1bcc)

在這裡再利用 的特性來進行與2基數FFT類似的化減方法,以降低演算法複雜度。

的特性來進行與2基數FFT類似的化減方法,以降低演算法複雜度。

在库利-图基算法裡,使用的基底(radix)越大,複數的乘法與記憶體的存取就越少,所帶來的好處不言而喻。但是隨之而來的就是實數的乘法與實數的加法也會增加,尤其計算單元的設計也就越複雜,對於可應用FFT之點數限制也就越嚴格。在表中我們可以看到在不同基底下所需的計算成本。

使用4096點FFT在不同基底下的計算量

| 動作 |

2基底 |

4基底 |

8基底

|

| 複數乘法

|

22528 |

15360 |

10752

|

| 實數乘法

|

0 |

0 |

8192

|

| 複數加法

|

49152 |

49152 |

49152

|

| 實數加法

|

0 |

0 |

8192

|

| 記憶體存取

|

49152 |

24576 |

16384

|

在DFT的公式中,我們重新定義x=[x(0),x(1),…,x(N-1)]T, X=[X(0),X(1),…,X(N-1)]T,則DFT可重寫為X=FN‧x。FN是一個N×N的DFT矩陣,其元素定義為[FN]ij=WNij(i,j ∈ [0,N-1]),當N=8時,我們可以得到以下的F8矩陣並且進一步將其拆解。

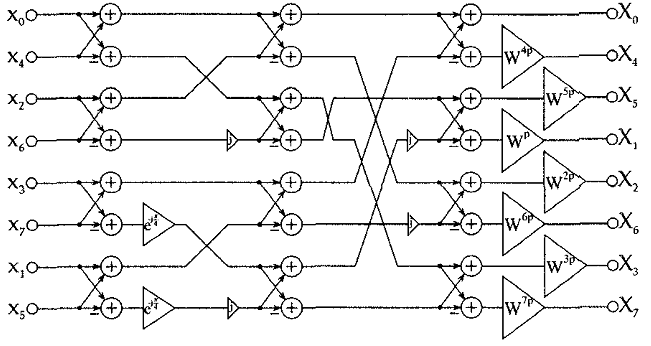

在拆解成三個矩陣相乘之後,我們可以將複數運算的數量從56個降至24個複數的加法。底下是8基底的SFG。要注意的是所有的輸出與輸入都是複數的形式,而輸出與輸入的排序也並非規律排列,此種排列方式是為了要達到接線的最佳化。

在2/8基底的演算法中,我們可以看到我們對於偶數項的輸出會使用2基底的分解法,對於奇數項的輸出採用8基底的分解法。這個做法充分利用了2基底與4基底擁有最少乘法數與加法數的特性。當使用了2基底的分解法後,偶數項的輸出如下所示。

奇數項的輸出則交由8基底分解來處理,如下四式所述。

![{\displaystyle C_{8k+1}=\sum _{n=0}^{{\frac {N}{8}}-1}{\begin{Bmatrix}[(x_{n}-x_{n+{\frac {N}{2}}})-j(x_{n+{\frac {N}{4}}}-x_{n+{\frac {3N}{4}}})]+W^{\frac {N}{8}}[(x_{n+{\frac {N}{8}}}-x_{n+{\frac {5N}{8}}})-j(x_{n+{\frac {3N}{8}}}-x_{n+{\frac {7N}{8}}})]\end{Bmatrix}}W^{8nk}W^{n}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/d60d9441ceabe5ec364c7ed4860c28e6e01dd685)

![{\displaystyle C_{8k+5}=\sum _{n=0}^{{\frac {N}{8}}-1}{\begin{Bmatrix}[(x_{n}-x_{n+{\frac {N}{2}}})-j(x_{n+{\frac {N}{4}}}-x_{n+{\frac {3N}{4}}})]-W^{\frac {N}{8}}[(x_{n+{\frac {N}{8}}}-x_{n+{\frac {5N}{8}}})-j(x_{n+{\frac {3N}{8}}}-x_{n+{\frac {7N}{8}}})]\end{Bmatrix}}W^{8nk}W^{5n}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/286f1e8ea80c9025c79dd90928d30fc333979a89)

![{\displaystyle C_{8k+3}=\sum _{n=0}^{{\frac {N}{8}}-1}{\begin{Bmatrix}[(x_{n}-x_{n+{\frac {N}{2}}})+j(x_{n+{\frac {N}{4}}}-x_{n+{\frac {3N}{4}}})]+W^{\frac {3N}{8}}[(x_{n+{\frac {N}{8}}}-x_{n+{\frac {5N}{8}}})+j(x_{n+{\frac {3N}{8}}}-x_{n+{\frac {7N}{8}}})]\end{Bmatrix}}W^{8nk}W^{3n}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/a0588921ec4688233fa8e96f55bdbf9e59808b72)

![{\displaystyle C_{8k+7}=\sum _{n=0}^{{\frac {N}{8}}-1}{\begin{Bmatrix}[(x_{n}-x_{n+{\frac {N}{2}}})+j(x_{n+{\frac {N}{4}}}-x_{n+{\frac {3N}{4}}})]-W^{\frac {3N}{8}}[(x_{n+{\frac {N}{8}}}-x_{n+{\frac {5N}{8}}})+j(x_{n+{\frac {3N}{8}}}-x_{n+{\frac {7N}{8}}})]\end{Bmatrix}}W^{8nk}W^{7n}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/d4bb9621b0ab6f2ae809b1f5e30363584a5b6023)

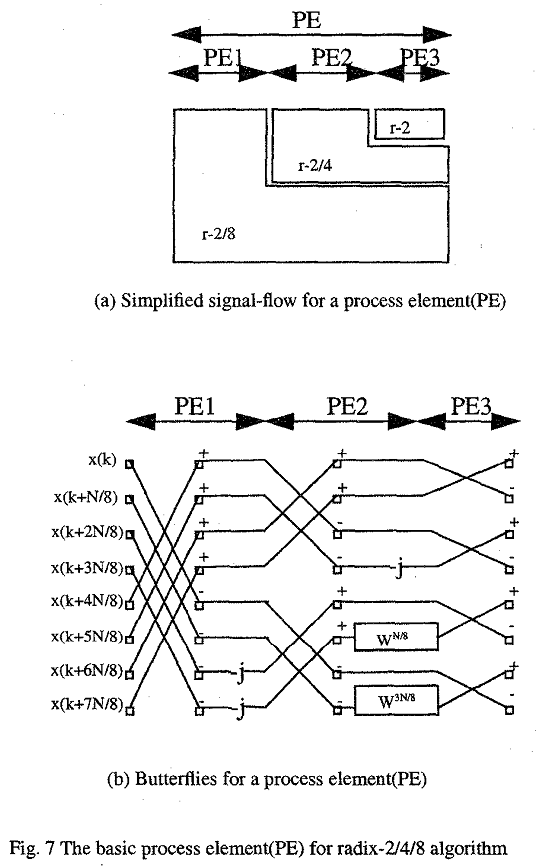

以上式子就是2/8基底的FFT快速演算法。在架構圖上可化為L型的蝴蝶運算架構,如下圖所示。

而下圖表示的是一個64點的FFT使用2/8基底的架構圖。雖然2/8基底的演算法縮減了 的乘法量,但是這種演算法最大的缺點是跟其他固定基底或是混合基底比較起來,他的架構較為不規則。所以在硬體上比4基底或是2基底更難實現。

的乘法量,但是這種演算法最大的缺點是跟其他固定基底或是混合基底比較起來,他的架構較為不規則。所以在硬體上比4基底或是2基底更難實現。

為了改進Radix 2/8在架構上的不規則性,我們在這裡做了一些修改,如下圖4.。此修改可讓架構更加規則,且所使用的加法器與乘法器數量更加減少,如下表所示。

8n點FFT在不同演算法下所需複數乘法量

| N=8n |

2基底 |

4基底 |

2/4混合基底 |

2/4/8基底

|

| 8

|

2 |

- |

2 |

0

|

| 64

|

98 |

76 |

72 |

48

|

| 512

|

1538 |

- |

1082 |

824

|

| 4096

|

18434 |

13996 |

12774 |

10168

|

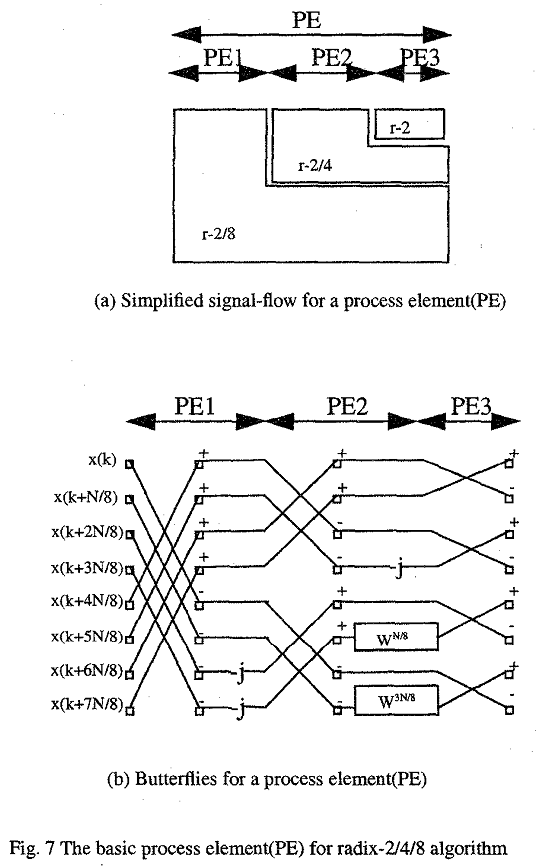

在這裡我們最小的運算單元稱為PE(Process Element),PE內部包含了2/8基底、2/4基底、2基底的運算,簡化過的信號處理流程與蝴蝶型架構圖可見下圖

基底的選擇越大會造成蝴蝶形架構更加複雜,控制電路也會複雜化。因此Shousheng He和Mats Torkelson在1996提出了一個2^2基底的FFT演算法,利用旋轉因子的特性: 。而–j的乘法基本上只需要將被乘數的實部虛部對調,然後將虛部加上負號即可,這樣的負數乘法被定義為'簡單乘法',因此可以用很簡單的硬體架構來實現。利用上面的特性,22基底FFT能用串接的方式將旋轉因子以4為單位對DFT公式進行拆解,將蝴蝶形架構層數降到log4N,大幅減少複數乘法器的用量,而同時卻維持了2基底蝴蝶形架構的簡單性,在效能上獲得改進。22基底DIF FFT演算法的拆解方法如下列公式所述:

。而–j的乘法基本上只需要將被乘數的實部虛部對調,然後將虛部加上負號即可,這樣的負數乘法被定義為'簡單乘法',因此可以用很簡單的硬體架構來實現。利用上面的特性,22基底FFT能用串接的方式將旋轉因子以4為單位對DFT公式進行拆解,將蝴蝶形架構層數降到log4N,大幅減少複數乘法器的用量,而同時卻維持了2基底蝴蝶形架構的簡單性,在效能上獲得改進。22基底DIF FFT演算法的拆解方法如下列公式所述:

N點DFT公式:

利用線性映射將n與k映射到三個維度上面

然後套用Common Factor Algorithm(CFA)

而蝴蝶型架構會變成以下形式

利用旋轉因子 的特性,可以觀察出

的特性,可以觀察出

再將此公式帶入原式中可以得到

![{\displaystyle X(k_{1}+2k_{2}+4k_{3})=\sum _{n_{3}=0}^{{\frac {N}{4}}-1}[H(k_{1},k_{2},n_{3})W_{N}^{n_{3}(k_{1}+2k_{2})}]W_{N}^{4n_{3}k_{3}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/db77541825977b92efa8e0ee66d1f77e66785c9e)

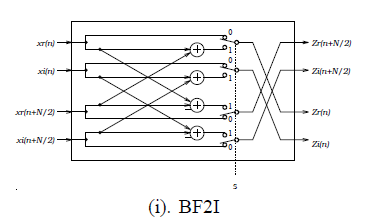

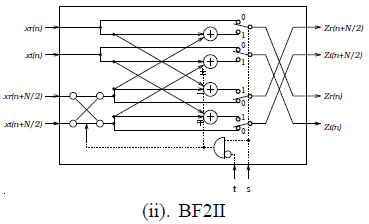

![{\displaystyle H(k_{1},k_{2},n_{3})={\begin{matrix}\underbrace {{\begin{matrix}BF2I\\\overbrace {[x(n_{3})+(-1)^{k_{1}}(n_{3}+{\frac {N}{2}})]} \end{matrix}}{\begin{matrix}\\\\+(-j)^{k_{1}+2k_{2}}\end{matrix}}{\begin{matrix}BF2I\\\overbrace {[x(n_{3}+{\frac {N}{4}})+(-1)^{k_{1}}(n_{3}+{\frac {3N}{4}})]} \end{matrix}}} \\BF2II\end{matrix}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/d09268954e4d0514d6d45a42e65d8f907b1408fb)

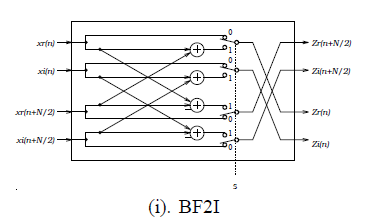

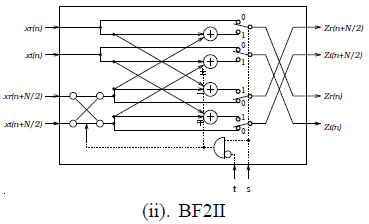

如上述公式所示,原本的DFT公式會被拆解成多個 ,而

,而 又可分為BF2I與BF2II兩個階層,分別會對應到之後所介紹的兩種硬體架構。

又可分為BF2I與BF2II兩個階層,分別會對應到之後所介紹的兩種硬體架構。

一個16點的DFT公式經過一次上面所述之拆解之後可得下面的FFT架構

可以看出上圖的架構保留了2基底的簡單架構,然而複數乘法卻降到每兩級才出現一次,也就是 次。而BF2I以及BF2II所對應的硬體架構下圖:

次。而BF2I以及BF2II所對應的硬體架構下圖:

其中BF2II硬體單元中左下角的交叉電路就是用來處理-j的乘法。

一個256點的FFT架構可以由下面的硬體來實現:

其中圖下方的為一7位元寬的計數器,而此架構的控制電路相當單純,只要將計數器的各個位元分別接上BF2I與BF2II單元即可。

下表將2基底、4基底與22基底演算法做一比較,可以發現22基底演算法所需要的乘法氣數量為2基底的一半,加法棄用量是4基底的一半,並維持一樣的記憶體用量和控制電路的簡單性。

乘法器與加法器數量比較

|

乘法數 |

加法數 |

記憶體大小 |

控制電路

|

| R2SDF

|

2(log4N-1) |

4log4N |

N-1 |

簡單

|

| R4SDF

|

log4N -1 |

8log4N |

N-1 |

中等

|

| R22SDF

|

log4N -1 |

4log4N |

N-1 |

簡單

|

如上所述,22演算法是將旋轉因子 視為一個簡單乘法,進而由公式以及硬體上的化簡獲得硬體需求上的改進。而藉由相同的概念,Shousheng He和Mats Torkelson進一步將旋轉因子

視為一個簡單乘法,進而由公式以及硬體上的化簡獲得硬體需求上的改進。而藉由相同的概念,Shousheng He和Mats Torkelson進一步將旋轉因子 的乘法化簡成一個簡單乘法,而化簡的方法將會在下面講解。

的乘法化簡成一個簡單乘法,而化簡的方法將會在下面講解。

乘法化簡

乘法化簡

[编辑]在2基數FFT演算法中的基本概念是利用旋轉因子 的對稱性,4基數演算法則是利用

的對稱性,4基數演算法則是利用

的特性。但是我們會發現在這些旋轉因子的對稱特性中─

的特性。但是我們會發現在這些旋轉因子的對稱特性中─

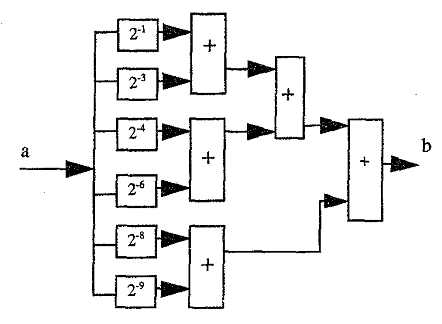

─並沒有被利用到。主要是因為 的乘法運算會讓整個FFT變得複雜,但是如果藉由近似的方法,我們便可以將此一運算化簡為12個加法。

的乘法運算會讓整個FFT變得複雜,但是如果藉由近似的方法,我們便可以將此一運算化簡為12個加法。

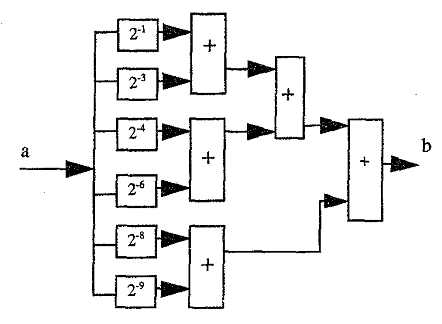

我們可以從上式注意到, 可以被近似為五個加法的結果,所以

可以被近似為五個加法的結果,所以 就可以被簡化為只有六個加法,再算入實部與虛部的計算,總共只需12個加法器就可以運用到此一簡化特性。

就可以被簡化為只有六個加法,再算入實部與虛部的計算,總共只需12個加法器就可以運用到此一簡化特性。

經由與22基底類似的推導,並用串接的方式將旋轉因子以8為單位對DFT公式進行拆解,23基底FFT演算法進一步將複數乘法器的用量縮減到log8N,並同時維持硬體架構的簡單性。

推導的方法與22基底相當類似。藉由這樣的方法,23基底能將乘法器的用量縮減到2基底的1/3,並同時維持一樣的記憶體用量以及控制電路的簡單性。

除了常在應用中見到與 相關基底的拆解法,對於更加一般性的

相關基底的拆解法,對於更加一般性的 點離散傅立葉變換問題,

我們也有辦法在理論上進行拆解,將問題化為數個

點離散傅立葉變換問題,

我們也有辦法在理論上進行拆解,將問題化為數個 與

與 點離散傅立葉變換問題,並可對計算量進行估計。

點離散傅立葉變換問題,並可對計算量進行估計。

而特別的是,透過互質在數論上的特性,對於 與

與 互質的情況,可以進一步節省一些運算,

在下面會特別分開討論。

互質的情況,可以進一步節省一些運算,

在下面會特別分開討論。

非互質

非互質

[编辑]為了避免之後的符號混淆,我們先將 置換為

置換為 ,也就是說接著要將

,也就是說接著要將 點離散傅立葉變換,

想辦法拆解為數個

點離散傅立葉變換,

想辦法拆解為數個 與

與 點離散傅立葉變換問題。

點離散傅立葉變換問題。

接著定義要拆分的問題,要拆分的問題為 點離散傅立葉變換,將

點離散傅立葉變換,將![{\displaystyle f[n]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/b176b3dbcced447341ad5ab70001ef0e3231062e) 轉換至

轉換至![{\displaystyle F[m]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/a8a330dbbd509e5cf62b65c35eadb49e4bac0679) :

:

![{\displaystyle F[m]=\sum _{n=0}^{N-1}e^{-i{\frac {2\pi }{N}}mn}f[n]\qquad m,n=0,1,\ldots ,N-1}](https://wikimedia.org/api/rest_v1/media/math/render/svg/8226440dbec103be06ba1ac90c7fd1f1eebfe8a3)

直觀地說,這個 點離散傅立葉變換,將由

點離散傅立葉變換,將由 作為參數的函數

作為參數的函數![{\displaystyle f[n]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/b176b3dbcced447341ad5ab70001ef0e3231062e) ,轉換成由

,轉換成由 作為參數的函數

作為參數的函數![{\displaystyle F[m]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/a8a330dbbd509e5cf62b65c35eadb49e4bac0679) ,

並且

,

並且 都有

都有 個可能的數值。

個可能的數值。

待定義好要拆分的問題,便可以開始討論如何進行拆分,基本概念是將有 個可能的數值的

個可能的數值的 ,

分別化為個使用兩個參數進行描述的函數

,

分別化為個使用兩個參數進行描述的函數![{\displaystyle m=[m_{1},m_{2}],n=[n_{1},n_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/2e49248674ab4caedcf579d417f5cd4ce4977b04) ,並藉此將原問題化為二維度離散傅立葉變換,

便可使用數個較小的離散傅立葉變換問題描述整個過程。

,並藉此將原問題化為二維度離散傅立葉變換,

便可使用數個較小的離散傅立葉變換問題描述整個過程。

而一種很直覺的轉換方式,便是透過將 分別除以

分別除以 ,

以商數與餘數來做為參數描述

,

以商數與餘數來做為參數描述 的值:

的值:

其中 作為將

作為將 除以

除以 的商數,與作為

的商數,與作為 除以

除以 的餘數的

的餘數的 相同,

具有

相同,

具有 個可能數值,同理

個可能數值,同理 與

與 有

有 個可能數值。

個可能數值。

將上述的參數代換及 帶入原式,可以得到:

帶入原式,可以得到:

![{\displaystyle F[m_{1}+m_{2}P_{2}]=\sum _{n_{1}=0}^{P_{2}-1}\sum _{n_{2}=0}^{P_{1}-1}e^{-i{\frac {2\pi }{P_{1}P_{2}}}(m_{1}+m_{2}P_{2})(n_{1}P_{1}+n_{2})}f[n_{1}P_{1}+n_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/f19dea8c1dbc711eff197a4f924dad8c8a1397e6)

將右式的指數部分乘開並分項化簡可以得到:

![{\displaystyle F[m_{1}+m_{2}P_{2}]=\sum _{n_{1}=0}^{P_{2}-1}\sum _{n_{2}=0}^{P_{1}-1}f[n_{1}P_{1}+n_{2}]e^{-i{\frac {2\pi }{P_{2}}}m_{1}n_{1}}e^{-i{\frac {2\pi }{P_{1}}}m_{2}n_{2}}e^{-i{\frac {2\pi }{P_{1}P_{2}}}m_{1}n_{2}}e^{-i2\pi m_{2}n_{1}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/18ab6bef3c01de064de149b9cceba27d124d1530)

最後透過 與

與 ,可以得到:

,可以得到:

![{\displaystyle F[m_{1}+m_{2}P_{2}]=\sum _{n_{2}=0}^{P_{1}-1}\sum _{n_{1}=0}^{P_{2}-1}f[n_{1}P_{1}+n_{2}]e^{-i{\frac {2\pi }{P_{2}}}m_{1}n_{1}}e^{-i{\frac {2\pi }{N}}m_{1}n_{2}}e^{-i{\frac {2\pi }{P_{1}}}m_{2}n_{2}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/fccb77176b70bfbb2b26bae879c5c3e07d7ac187)

觀察上式,並加上括號輔助釐清運算順序我們可以得到:

![{\displaystyle F[m_{1}+m_{2}P_{2}]=\sum _{n_{2}=0}^{P_{1}-1}\left\{\left\{\sum _{n_{1}=0}^{P_{2}-1}f[n_{1}P_{1}+n_{2}]e^{-i{\frac {2\pi }{P_{2}}}m_{1}n_{1}}\right\}e^{-i{\frac {2\pi }{N}}m_{1}n_{2}}\right\}e^{-i{\frac {2\pi }{P_{1}}}m_{2}n_{2}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/768d038281d68b49128e94a95b1f6c22dce3bd3b)

最內層的運算可以視為將雙參數函數![{\displaystyle f[n_{1},n_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/029e8f5137ccba4e89cc0557dda63e9db2749d24) 中的一個參數

中的一個參數 ,透過離散傅立葉變換取代為由

,透過離散傅立葉變換取代為由 描述,

得到一個新函數

描述,

得到一個新函數![{\displaystyle G_{1}[m_{1},n_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/e0d95b38d3c00994c74f97370efeb8effbfbd328) (這步因為對每個不同

(這步因為對每個不同 ,都需要做一次將

,都需要做一次將 取代為

取代為 的轉換,

共需要

的轉換,

共需要 個

個 點離散傅立葉變換):

點離散傅立葉變換):

![{\displaystyle F[m_{1}+m_{2}P_{2}]=\sum _{n_{2}=0}^{P_{1}-1}\left\{G_{1}[m_{1},n_{2}]e^{-i{\frac {2\pi }{N}}m_{1}n_{2}}\right\}e^{-i{\frac {2\pi }{P_{1}}}m_{2}n_{2}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/b8b0a9b42a0a9e4f3f3734e7db2801e443507227)

下一層的運算則可視為單純的乘法,將![{\displaystyle G_{1}[m_{1},n_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/e0d95b38d3c00994c74f97370efeb8effbfbd328) 與

與 相乘,得到

相乘,得到![{\displaystyle G_{2}[m_{1},n_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/84f9e03fd35589b0f6ed9c9b128d03dafccc26c5) (這步需要的計算量視

(這步需要的計算量視 的特殊性而會有變化):

的特殊性而會有變化):

![{\displaystyle F[m_{1}+m_{2}P_{2}]=\sum _{n_{2}=0}^{P_{1}-1}G_{2}[m_{1},n_{2}]e^{-i{\frac {2\pi }{P_{1}}}m_{2}n_{2}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/4e73789287fad4cabb3098c7a4ea0b3cc4bfcca8)

最後的運算可以視為將函數![{\displaystyle G_{2}[m_{1},n_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/84f9e03fd35589b0f6ed9c9b128d03dafccc26c5) 中

中 ,透過離散傅立葉變換取代為由

,透過離散傅立葉變換取代為由 描述,

得到一個新函數

描述,

得到一個新函數![{\displaystyle G_{3}[m_{1},m_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/0377a34d0f0130264ed76f35e6b5231f0dcc1146) (這步因為對每個不同

(這步因為對每個不同 ,都需要做一次將

,都需要做一次將 取代為

取代為 的轉換,

共需要

的轉換,

共需要 個

個 點離散傅立葉變換):

點離散傅立葉變換):

![{\displaystyle F[m(=m_{1}+m_{2}P_{2})]=G_{3}[m_{1},m_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/df4585d6ad62008c07870077bbfe0df7e7aef703)

就成功僅使用 與

與 點離散傅立葉變換,描述了原先的

點離散傅立葉變換,描述了原先的 點離散傅立葉變換。

點離散傅立葉變換。

而在這樣的分解下,我們使用了 個

個 點離散傅立葉變換與

點離散傅立葉變換與 個

個 點離散傅立葉變換與一些額外的乘法,

並且這些額外使用的複數乘法

點離散傅立葉變換與一些額外的乘法,

並且這些額外使用的複數乘法![{\displaystyle G_{1}[m_{1},n_{2}]\times e^{-i{\frac {2\pi }{N}}m_{1}n_{2}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/3d791a975db7159ff83fbfccd30d402545c32e90) ,

在電腦的運算架構中,如果

,

在電腦的運算架構中,如果 是

是 的倍數則不需要使用乘法,

如果

的倍數則不需要使用乘法,

如果 是

是 的倍數則僅需兩個實數乘法,

其他則需三個實數乘法,所以總運算量可以如下方式表示:

的倍數則僅需兩個實數乘法,

其他則需三個實數乘法,所以總運算量可以如下方式表示:

其中 是

是 傅立葉所需乘法數,

傅立葉所需乘法數, 是

是 傅立葉所需乘法數,

傅立葉所需乘法數,

是需三個實數乘法

是需三個實數乘法 組合個數,

組合個數, 是需兩個實數乘法

是需兩個實數乘法 組合個數。

組合個數。

而常見以 為基底的分解則是為了使離散傅立葉變換所需乘法數為零,這樣就僅需考慮上面提到的額外乘法,可以提高效率也有較簡單的結構。

為基底的分解則是為了使離散傅立葉變換所需乘法數為零,這樣就僅需考慮上面提到的額外乘法,可以提高效率也有較簡單的結構。

互質

互質

[编辑]在 互質的情況下,仍是採取和上面相近的思路來將問題進行拆分,首先,為了避免之後的符號混淆,我們同樣將

互質的情況下,仍是採取和上面相近的思路來將問題進行拆分,首先,為了避免之後的符號混淆,我們同樣將 置換為

置換為 。

。

接著同樣定義要拆分的問題:

![{\displaystyle F[m]=\sum _{n=0}^{N-1}e^{-i{\frac {2\pi }{N}}mn}f[n]\qquad m,n=0,1,\ldots ,N-1}](https://wikimedia.org/api/rest_v1/media/math/render/svg/8226440dbec103be06ba1ac90c7fd1f1eebfe8a3)

接著就是和上面的算法有最大差異的部分,在將 化為個使用兩個參數進行描述的函數

化為個使用兩個參數進行描述的函數![{\displaystyle m=[m_{1},m_{2}],n=[n_{1},n_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/2e49248674ab4caedcf579d417f5cd4ce4977b04) 時,

最直覺的作法便是使用商數和餘數,但在

時,

最直覺的作法便是使用商數和餘數,但在 互質的情況下,可以有一些其他更具技巧性的選擇。

互質的情況下,可以有一些其他更具技巧性的選擇。

當 互質,對所有

互質,對所有 我們可以找到唯一且不重複的一組

我們可以找到唯一且不重複的一組 使得:

使得:

其中 ,代表取餘數的意思,

,代表取餘數的意思, 是一個整數。

是一個整數。

例如假設 ,則

,則 對應到的

對應到的 就是

就是 ,

有

,

有 。

。

並且對所有 的組合(有

的組合(有 組),都對應到一個特定不重複的

組),都對應到一個特定不重複的 。

。

同理我們可以把 表示為

表示為 的雙參數函數:

的雙參數函數:

將上述的參數代換及 帶入原式,可以得到:

帶入原式,可以得到:

![{\displaystyle F[((m_{1}P_{1}+m_{2}P_{2}))_{N}]=\sum _{n_{1}=0}^{P_{2}-1}\sum _{n_{2}=0}^{P_{1}-1}e^{-i{\frac {2\pi }{N}}(m_{1}P_{1}+m_{2}P_{2}+c_{2}N)(n_{1}P_{1}+n_{2}P_{2}+c_{1}N)}f[((n_{1}P_{1}+n_{2}P_{2}))_{N}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/1276247def7d40452a8976094630c539ff1bd5a1)

接著透過一次的展開化簡及應用 可得:

可得:

![{\displaystyle {\begin{aligned}F[((m_{1}P_{1}+m_{2}P_{2}))_{N}]&=\sum _{n_{1}=0}^{P_{2}-1}\sum _{n_{2}=0}^{P_{1}-1}e^{-i{\frac {2\pi }{N}}(m_{1}P_{1}+m_{2}P_{2})(n_{1}P_{1}+n_{2}P_{2})}e^{-i2\pi c_{2}(n_{1}P_{1}+n_{2}P_{2}+c_{1}N)}e^{-i2\pi c_{1}(m_{1}P_{1}+m_{2}P_{2}+c_{2}N)}e^{-i2\pi c_{1}c_{2}N}f[((n_{1}P_{1}+n_{2}P_{2}))_{N}]\\&=\sum _{n_{1}=0}^{P_{2}-1}\sum _{n_{2}=0}^{P_{1}-1}e^{-i{\frac {2\pi }{N}}(m_{1}P_{1}+m_{2}P_{2})(n_{1}P_{1}+n_{2}P_{2})}f[((n_{1}P_{1}+n_{2}P_{2}))_{N}]\end{aligned}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/9cc3e0a72f2544412093e6b520ef7edd688f74c4)

再將 帶入並再透過一次的展開化簡及應用

帶入並再透過一次的展開化簡及應用 可得:

可得:

![{\displaystyle {\begin{aligned}F[((m_{1}P_{1}+m_{2}P_{2}))_{N}]&=\sum _{n_{1}=0}^{P_{2}-1}\sum _{n_{2}=0}^{P_{1}-1}f[((n_{1}P_{1}+n_{2}P_{2}))_{N}]e^{-i{\frac {2\pi }{P_{2}}}m_{1}P_{1}n_{1}}e^{-i{\frac {2\pi }{P_{1}}}m_{2}P_{2}n_{2}}e^{-i2\pi m_{1}n_{2}}e^{-i2\pi m_{2}n_{1}}\\&=\sum _{n_{1}=0}^{P_{2}-1}\sum _{n_{2}=0}^{P_{1}-1}f[((n_{1}P_{1}+n_{2}P_{2}))_{N}]e^{-i{\frac {2\pi }{P_{2}}}m_{1}P_{1}n_{1}}e^{-i{\frac {2\pi }{P_{1}}}m_{2}P_{2}n_{2}}\end{aligned}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/3de70c9313d5ee468f964f4447a6dbad62b0a647)

觀察上式,並加上括號輔助釐清運算順序我們可以得到:

![{\displaystyle F[((m_{1}P_{1}+m_{2}P_{2}))_{N}]=\sum _{n_{2}=0}^{P_{1}-1}\left\{\sum _{n_{1}=0}^{P_{2}-1}f[((n_{1}P_{1}+n_{2}P_{2}))_{N}]e^{-i{\frac {2\pi }{P_{2}}}m_{1}P_{1}n_{1}}\right\}e^{-i{\frac {2\pi }{P_{1}}}m_{2}P_{2}n_{2}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/e74556a86839387afcf933f309d6d12aa954cb28)

內層的運算可以視為將雙參數函數![{\displaystyle f[((n_{1}P_{1}+n_{2}P_{2}))_{N}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/e3e80c7b39d1c027c9873fe57feb76f1ee7632d1) 中的一個參數

中的一個參數 ,

透過離散傅立葉變換取代為由一個與

,

透過離散傅立葉變換取代為由一個與 有關的變數

有關的變數 描述,

得到一個新函數

描述,

得到一個新函數![{\displaystyle G_{1}[m_{3},n_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/c5169569e417019b3ab4c0aeb5bf2a384aa68307) (這步因為對每個不同

(這步因為對每個不同 ,都需要做一次將

,都需要做一次將 取代為

取代為 的轉換,

共需要

的轉換,

共需要 個

個 點離散傅立葉變換):

點離散傅立葉變換):

![{\displaystyle F[((m_{1}P_{1}+m_{2}P_{2}))_{N}]=\sum _{n_{2}=0}^{P_{1}-1}G_{1}[m_{3},n_{2}]e^{-i{\frac {2\pi }{P_{1}}}m_{2}P_{2}n_{2}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/b1d6ab6f9dd4affdce3d9499aedd1d1082616a7e)

外層的運算可以視為將函數![{\displaystyle G_{1}[m_{3},n_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/c5169569e417019b3ab4c0aeb5bf2a384aa68307) 中的參數

中的參數 ,

透過離散傅立葉變換取代為由一個與

,

透過離散傅立葉變換取代為由一個與 有關的變數

有關的變數 描述,

得到一個新函數

描述,

得到一個新函數![{\displaystyle G_{2}[m_{3},m_{4}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/0232af78b3229760d65e779679576263ca9d48ee) (這步因為對每個不同

(這步因為對每個不同 ,都需要做一次將

,都需要做一次將 取代為

取代為 的轉換,

共需要

的轉換,

共需要 個

個 點離散傅立葉變換):

點離散傅立葉變換):

![{\displaystyle F[m]=F[((m_{1}P_{1}+m_{2}P_{2}))_{N}]=G_{2}[m_{3},m_{4}]=G_{2}[((m_{1}P_{1}))_{P_{2}},((m_{2}P_{2}))_{P_{1}}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/062237ab486830ce263acd942e5e4d6496e428c5)

最後透過 與

與 在不同

在不同 時的點點數值對應關係,

就成功僅使用

時的點點數值對應關係,

就成功僅使用 與

與 點離散傅立葉變換,描述了原先的

點離散傅立葉變換,描述了原先的 點離散傅立葉變換。

點離散傅立葉變換。

而這個方法透過聰明的選取表達 的方式,使得拆解的過程中完全不需要多餘的乘法運算,

總運算量可以簡單表示為:

的方式,使得拆解的過程中完全不需要多餘的乘法運算,

總運算量可以簡單表示為:

其中 是

是 傅立葉所需乘法數,

傅立葉所需乘法數, 是

是 傅立葉所需乘法數。

傅立葉所需乘法數。

雖然這個方法可以較上面的方法節省運算量,

但這個方法也牽涉較為複雜的 與

與 轉換,較為不直覺且不易理解,

也會遇到許多需要取餘數的運算,可能會需要較大的空間建表進行查表法。

轉換,較為不直覺且不易理解,

也會遇到許多需要取餘數的運算,可能會需要較大的空間建表進行查表法。

最後關於實際上要如何求得 與

與 的轉換關係,

可以先透過輾轉相除法取得一對特定的

的轉換關係,

可以先透過輾轉相除法取得一對特定的 使得:

使得:

然後我們可以知道對於任意整數 有:

有:

然後就可以得到:

滿足:

- Widhe, T., J. Melander, et al. (1997). Design of efficient radix-8 butterfly PEs for VLSI. Circuits and Systems, 1997. ISCAS '97., Proceedings of 1997 IEEE International Symposium on.

- Lihong, J., G. Yonghong, et al. (1998). A new VLSI-oriented FFT algorithm and implementation. ASIC Conference 1998. Proceedings. Eleventh Annual IEEE International.

- Duhamel, P. and H. Hollmann (1984). "Split-radix FFT algorithm." Electronics Letters 20(1): 14-16.

- Vetterli, M. and P. Duhamel (1989). "Split-radix algorithms for length-pm DFT's." Acoustics, Speech and Signal Processing, IEEE Transactions on 37(1): 57-64.

- Richards, M. A. (1988). "On hardware implementation of the split-radix FFT." Acoustics, Speech and Signal Processing, IEEE Transactions on 36(10): 1575-1581.

- Shousheng, H. and M. Torkelson (1996). A new approach to pipeline FFT processor. Parallel Processing Symposium, 1996., Proceedings of IPPS '96, The 10th International.

- Shousheng, H. and M. Torkelson (1998). Designing pipeline FFT processor for OFDM (de)modulation. Signals, Systems, and Electronics, 1998. ISSSE 98. 1998 URSI International Symposium on.

![{\displaystyle X[k]=\sum _{n=0}^{N-1}x[n]e^{-j(2\pi {\frac {nk}{N}})}\qquad k=0,1,\ldots ,N-1}](https://wikimedia.org/api/rest_v1/media/math/render/svg/8c1bc58d53eca4db8e882d962288d85cdeca7b9e)

![{\displaystyle =\sum _{n\ even}x[n]W_{N}^{nk}+\sum _{n\ odd}x[n]W_{N}^{nk}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/fd189ceb0840b111ad6650a8f3c346005800e4b2)

![{\displaystyle =\sum _{r=0}^{(N/2)-1}x[2r]W_{N}^{2rk}+\sum _{r=0}^{(N/2)-1}x[2r+1]W_{N}^{(2r+1)k}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/d07a0c81f453e445996a3e0435257d6e8798d447)

![{\displaystyle =\sum _{r=0}^{(N/2)-1}x[2r]W_{N}^{2rk}+W_{N}^{k}\sum _{r=0}^{(N/2)-1}x[2r+1]W_{N}^{2rk}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/03b58a209e5dc96cacbe5427d112edfa4b6b404e)

![{\displaystyle =\sum _{r=0}^{(N/2)-1}x[2r]W_{N/2}^{rk}+W_{N}^{k}\sum _{r=0}^{(N/2)-1}x[2r+1]W_{N/2}^{rk}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/fd254ec25ac6c8b112c96dec2a91b1445fa53257)

![{\displaystyle =G[k]+W_{N}^{k}H[k]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/53bf0cddeac84818155040de470b85dffe948b4e)

![{\displaystyle {\begin{cases}G[k+{\frac {N}{2}}]=G[k]\\H[k+{\frac {N}{2}}]=H[k]\end{cases}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/00ecf779771f585dedf8e3c907e09ebd2f202592)

![{\displaystyle X[2r]=\sum _{n=0}^{N-1}x[n]W_{N}^{n(2r)}\ r=0,1,\cdots ,{\frac {N}{2}}-1}](https://wikimedia.org/api/rest_v1/media/math/render/svg/d2e7461d1b092e029a7bb2af92dccdfd431f7da0)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}x[n]W_{N}^{2nr}+\sum _{n={\frac {N}{2}}}^{N-1}x[n]W_{N}^{2nr}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/801a6470581d07a5f484bbd4b0434f59e32e934e)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}x[n]W_{N}^{2nr}+\sum _{n=0}^{{\frac {N}{2}}-1}x[n+{\frac {N}{2}}]W_{N}^{2r[n+{\frac {N}{2}}]}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/ec893531fefe43082191e7997d6485e87d2b69b0)

![{\displaystyle {\color {Gray}\because W_{N}^{2r[n+{\frac {N}{2}}]}=W_{N}^{2rn}W_{N}^{rN}=W_{N}^{2rn}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/7dad33e79d93241676845acd8cc89b3ff7e5805e)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}x[n]W_{N}^{2rn}+\sum _{n=0}^{{\frac {N}{2}}-1}x[n+{\frac {N}{2}}]W_{N}^{2rn}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/cd9f6e7fcb74256acbca841551e919ef0dbe57d6)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}(x[n]+x[n+{\frac {N}{2}}])W_{\frac {N}{2}}^{rn}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/630f613aad2e2c1cff0a9feea68373e9f0bcda75)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}g[n]W_{\frac {N}{2}}^{rn}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/a0a497711c3349d02cf3fed19e31284de68f4e85)

![{\displaystyle X[2r+1]=\sum _{n=0}^{N-1}x[n]W_{N}^{n(2r+1)}\ r=0,1,\cdots ,{\frac {N}{2}}-1}](https://wikimedia.org/api/rest_v1/media/math/render/svg/2e846f60e833bf7b4c9c564eaf91833c7c4df8df)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}x[n]W_{N}^{n(2r+1)}+\sum _{n={\frac {N}{2}}}^{N-1}x[n]W_{N}^{n(2r+1)}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/f3bec22826122b8c8b86ddc2c63a48c9b05f77e8)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}x[n]W_{N}^{n(2r+1)}+\sum _{n=0}^{{\frac {N}{2}}-1}x[n+{\frac {N}{2}}]W_{N}^{(2r+1)[n+{\frac {N}{2}}]}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/0ba17694e21aaba1b37bf209160d83891c396b1e)

![{\displaystyle {\color {Gray}\because W_{N}^{(2r+1)[n+{\frac {N}{2}}]}=W_{N}^{(2r+1)n}W_{N}^{(2r+1){\frac {N}{2}}}=-W_{N}^{(2r+1)n}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/4d8bb52435fc07264d500482ffec6598856023eb)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}x[n]W_{N}^{(2r+1)n}-\sum _{n=0}^{{\frac {N}{2}}-1}x[n+{\frac {N}{2}}]W_{N}^{(2r+1)n}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/0fbc417eb823a092b4678647586ba94b939ba563)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}(x[n]-x[n+{\frac {N}{2}}])W_{N}^{n(2r+1)}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/b71d627069159f2180bdfc93c021c0a043fdca0b)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}(x[n]-x[n+{\frac {N}{2}}])W_{N}^{n}W_{\frac {N}{2}}^{nr}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/ddaa565a4815dbd7599bc1cad89e8cb86690d0cc)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{2}}-1}(h[n]W_{N}^{n})W_{\frac {N}{2}}^{rn}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/5a60b843e1adbb6c6ad5bc9dcdd3bbaf4d98f6f5)

![{\displaystyle =\sum _{n=0}^{{\frac {N}{4}}-1}x[4n+0]W_{N}^{(4n+0)k}+\sum _{n=0}^{{\frac {N}{4}}-1}x[4n+1]W_{N}^{(4n+1)k}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/13719c6b6c1cb7e06dab16b2e0e0fbfa4f592a2c)

![{\displaystyle +\sum _{n=0}^{{\frac {N}{4}}-1}x[4n+2]W_{N}^{(4n+2)k}+\sum _{n=0}^{{\frac {N}{4}}-1}x[4n+3]W_{N}^{(4n+3)k}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/a3a0f9401cc8ea8aa63fe510967aa6d40e2bd46c)

![{\displaystyle =W_{N}^{0}\sum _{n=0}^{{\frac {N}{4}}-1}x[4n+0]W_{\frac {N}{4}}^{nk}+W_{N}^{1k}\sum _{n=0}^{{\frac {N}{4}}-1}x[4n+1]W_{\frac {N}{4}}^{nk}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/519a556d3e2ef2460c4166d30864065b29220d11)

![{\displaystyle +W_{N}^{2k}\sum _{n=0}^{{\frac {N}{4}}-1}x[4n+2]W_{\frac {N}{4}}^{nk}+W_{N}^{3k}\sum _{n=0}^{{\frac {N}{4}}-1}x[4n+3]W_{\frac {N}{4}}^{nk}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/cbd2e5ec944fe84a6edf79ef26b9ea82436a1bcc)

![{\displaystyle C_{8k+1}=\sum _{n=0}^{{\frac {N}{8}}-1}{\begin{Bmatrix}[(x_{n}-x_{n+{\frac {N}{2}}})-j(x_{n+{\frac {N}{4}}}-x_{n+{\frac {3N}{4}}})]+W^{\frac {N}{8}}[(x_{n+{\frac {N}{8}}}-x_{n+{\frac {5N}{8}}})-j(x_{n+{\frac {3N}{8}}}-x_{n+{\frac {7N}{8}}})]\end{Bmatrix}}W^{8nk}W^{n}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/d60d9441ceabe5ec364c7ed4860c28e6e01dd685)

![{\displaystyle C_{8k+5}=\sum _{n=0}^{{\frac {N}{8}}-1}{\begin{Bmatrix}[(x_{n}-x_{n+{\frac {N}{2}}})-j(x_{n+{\frac {N}{4}}}-x_{n+{\frac {3N}{4}}})]-W^{\frac {N}{8}}[(x_{n+{\frac {N}{8}}}-x_{n+{\frac {5N}{8}}})-j(x_{n+{\frac {3N}{8}}}-x_{n+{\frac {7N}{8}}})]\end{Bmatrix}}W^{8nk}W^{5n}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/286f1e8ea80c9025c79dd90928d30fc333979a89)

![{\displaystyle C_{8k+3}=\sum _{n=0}^{{\frac {N}{8}}-1}{\begin{Bmatrix}[(x_{n}-x_{n+{\frac {N}{2}}})+j(x_{n+{\frac {N}{4}}}-x_{n+{\frac {3N}{4}}})]+W^{\frac {3N}{8}}[(x_{n+{\frac {N}{8}}}-x_{n+{\frac {5N}{8}}})+j(x_{n+{\frac {3N}{8}}}-x_{n+{\frac {7N}{8}}})]\end{Bmatrix}}W^{8nk}W^{3n}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/a0588921ec4688233fa8e96f55bdbf9e59808b72)

![{\displaystyle C_{8k+7}=\sum _{n=0}^{{\frac {N}{8}}-1}{\begin{Bmatrix}[(x_{n}-x_{n+{\frac {N}{2}}})+j(x_{n+{\frac {N}{4}}}-x_{n+{\frac {3N}{4}}})]-W^{\frac {3N}{8}}[(x_{n+{\frac {N}{8}}}-x_{n+{\frac {5N}{8}}})+j(x_{n+{\frac {3N}{8}}}-x_{n+{\frac {7N}{8}}})]\end{Bmatrix}}W^{8nk}W^{7n}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/d4bb9621b0ab6f2ae809b1f5e30363584a5b6023)

![{\displaystyle X(k_{1}+2k_{2}+4k_{3})=\sum _{n_{3}=0}^{{\frac {N}{4}}-1}[H(k_{1},k_{2},n_{3})W_{N}^{n_{3}(k_{1}+2k_{2})}]W_{N}^{4n_{3}k_{3}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/db77541825977b92efa8e0ee66d1f77e66785c9e)

![{\displaystyle H(k_{1},k_{2},n_{3})={\begin{matrix}\underbrace {{\begin{matrix}BF2I\\\overbrace {[x(n_{3})+(-1)^{k_{1}}(n_{3}+{\frac {N}{2}})]} \end{matrix}}{\begin{matrix}\\\\+(-j)^{k_{1}+2k_{2}}\end{matrix}}{\begin{matrix}BF2I\\\overbrace {[x(n_{3}+{\frac {N}{4}})+(-1)^{k_{1}}(n_{3}+{\frac {3N}{4}})]} \end{matrix}}} \\BF2II\end{matrix}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/d09268954e4d0514d6d45a42e65d8f907b1408fb)

![{\displaystyle f[n]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/b176b3dbcced447341ad5ab70001ef0e3231062e)

![{\displaystyle F[m]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/a8a330dbbd509e5cf62b65c35eadb49e4bac0679)

![{\displaystyle F[m]=\sum _{n=0}^{N-1}e^{-i{\frac {2\pi }{N}}mn}f[n]\qquad m,n=0,1,\ldots ,N-1}](https://wikimedia.org/api/rest_v1/media/math/render/svg/8226440dbec103be06ba1ac90c7fd1f1eebfe8a3)

![{\displaystyle m=[m_{1},m_{2}],n=[n_{1},n_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/2e49248674ab4caedcf579d417f5cd4ce4977b04)

![{\displaystyle F[m_{1}+m_{2}P_{2}]=\sum _{n_{1}=0}^{P_{2}-1}\sum _{n_{2}=0}^{P_{1}-1}e^{-i{\frac {2\pi }{P_{1}P_{2}}}(m_{1}+m_{2}P_{2})(n_{1}P_{1}+n_{2})}f[n_{1}P_{1}+n_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/f19dea8c1dbc711eff197a4f924dad8c8a1397e6)

![{\displaystyle F[m_{1}+m_{2}P_{2}]=\sum _{n_{1}=0}^{P_{2}-1}\sum _{n_{2}=0}^{P_{1}-1}f[n_{1}P_{1}+n_{2}]e^{-i{\frac {2\pi }{P_{2}}}m_{1}n_{1}}e^{-i{\frac {2\pi }{P_{1}}}m_{2}n_{2}}e^{-i{\frac {2\pi }{P_{1}P_{2}}}m_{1}n_{2}}e^{-i2\pi m_{2}n_{1}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/18ab6bef3c01de064de149b9cceba27d124d1530)

![{\displaystyle F[m_{1}+m_{2}P_{2}]=\sum _{n_{2}=0}^{P_{1}-1}\sum _{n_{1}=0}^{P_{2}-1}f[n_{1}P_{1}+n_{2}]e^{-i{\frac {2\pi }{P_{2}}}m_{1}n_{1}}e^{-i{\frac {2\pi }{N}}m_{1}n_{2}}e^{-i{\frac {2\pi }{P_{1}}}m_{2}n_{2}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/fccb77176b70bfbb2b26bae879c5c3e07d7ac187)

![{\displaystyle F[m_{1}+m_{2}P_{2}]=\sum _{n_{2}=0}^{P_{1}-1}\left\{\left\{\sum _{n_{1}=0}^{P_{2}-1}f[n_{1}P_{1}+n_{2}]e^{-i{\frac {2\pi }{P_{2}}}m_{1}n_{1}}\right\}e^{-i{\frac {2\pi }{N}}m_{1}n_{2}}\right\}e^{-i{\frac {2\pi }{P_{1}}}m_{2}n_{2}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/768d038281d68b49128e94a95b1f6c22dce3bd3b)

![{\displaystyle f[n_{1},n_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/029e8f5137ccba4e89cc0557dda63e9db2749d24)

![{\displaystyle G_{1}[m_{1},n_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/e0d95b38d3c00994c74f97370efeb8effbfbd328)

![{\displaystyle F[m_{1}+m_{2}P_{2}]=\sum _{n_{2}=0}^{P_{1}-1}\left\{G_{1}[m_{1},n_{2}]e^{-i{\frac {2\pi }{N}}m_{1}n_{2}}\right\}e^{-i{\frac {2\pi }{P_{1}}}m_{2}n_{2}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/b8b0a9b42a0a9e4f3f3734e7db2801e443507227)

![{\displaystyle G_{2}[m_{1},n_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/84f9e03fd35589b0f6ed9c9b128d03dafccc26c5)

![{\displaystyle F[m_{1}+m_{2}P_{2}]=\sum _{n_{2}=0}^{P_{1}-1}G_{2}[m_{1},n_{2}]e^{-i{\frac {2\pi }{P_{1}}}m_{2}n_{2}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/4e73789287fad4cabb3098c7a4ea0b3cc4bfcca8)

![{\displaystyle G_{3}[m_{1},m_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/0377a34d0f0130264ed76f35e6b5231f0dcc1146)

![{\displaystyle F[m(=m_{1}+m_{2}P_{2})]=G_{3}[m_{1},m_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/df4585d6ad62008c07870077bbfe0df7e7aef703)

![{\displaystyle G_{1}[m_{1},n_{2}]\times e^{-i{\frac {2\pi }{N}}m_{1}n_{2}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/3d791a975db7159ff83fbfccd30d402545c32e90)

![{\displaystyle F[((m_{1}P_{1}+m_{2}P_{2}))_{N}]=\sum _{n_{1}=0}^{P_{2}-1}\sum _{n_{2}=0}^{P_{1}-1}e^{-i{\frac {2\pi }{N}}(m_{1}P_{1}+m_{2}P_{2}+c_{2}N)(n_{1}P_{1}+n_{2}P_{2}+c_{1}N)}f[((n_{1}P_{1}+n_{2}P_{2}))_{N}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/1276247def7d40452a8976094630c539ff1bd5a1)

![{\displaystyle {\begin{aligned}F[((m_{1}P_{1}+m_{2}P_{2}))_{N}]&=\sum _{n_{1}=0}^{P_{2}-1}\sum _{n_{2}=0}^{P_{1}-1}e^{-i{\frac {2\pi }{N}}(m_{1}P_{1}+m_{2}P_{2})(n_{1}P_{1}+n_{2}P_{2})}e^{-i2\pi c_{2}(n_{1}P_{1}+n_{2}P_{2}+c_{1}N)}e^{-i2\pi c_{1}(m_{1}P_{1}+m_{2}P_{2}+c_{2}N)}e^{-i2\pi c_{1}c_{2}N}f[((n_{1}P_{1}+n_{2}P_{2}))_{N}]\\&=\sum _{n_{1}=0}^{P_{2}-1}\sum _{n_{2}=0}^{P_{1}-1}e^{-i{\frac {2\pi }{N}}(m_{1}P_{1}+m_{2}P_{2})(n_{1}P_{1}+n_{2}P_{2})}f[((n_{1}P_{1}+n_{2}P_{2}))_{N}]\end{aligned}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/9cc3e0a72f2544412093e6b520ef7edd688f74c4)

![{\displaystyle {\begin{aligned}F[((m_{1}P_{1}+m_{2}P_{2}))_{N}]&=\sum _{n_{1}=0}^{P_{2}-1}\sum _{n_{2}=0}^{P_{1}-1}f[((n_{1}P_{1}+n_{2}P_{2}))_{N}]e^{-i{\frac {2\pi }{P_{2}}}m_{1}P_{1}n_{1}}e^{-i{\frac {2\pi }{P_{1}}}m_{2}P_{2}n_{2}}e^{-i2\pi m_{1}n_{2}}e^{-i2\pi m_{2}n_{1}}\\&=\sum _{n_{1}=0}^{P_{2}-1}\sum _{n_{2}=0}^{P_{1}-1}f[((n_{1}P_{1}+n_{2}P_{2}))_{N}]e^{-i{\frac {2\pi }{P_{2}}}m_{1}P_{1}n_{1}}e^{-i{\frac {2\pi }{P_{1}}}m_{2}P_{2}n_{2}}\end{aligned}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/3de70c9313d5ee468f964f4447a6dbad62b0a647)

![{\displaystyle F[((m_{1}P_{1}+m_{2}P_{2}))_{N}]=\sum _{n_{2}=0}^{P_{1}-1}\left\{\sum _{n_{1}=0}^{P_{2}-1}f[((n_{1}P_{1}+n_{2}P_{2}))_{N}]e^{-i{\frac {2\pi }{P_{2}}}m_{1}P_{1}n_{1}}\right\}e^{-i{\frac {2\pi }{P_{1}}}m_{2}P_{2}n_{2}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/e74556a86839387afcf933f309d6d12aa954cb28)

![{\displaystyle f[((n_{1}P_{1}+n_{2}P_{2}))_{N}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/e3e80c7b39d1c027c9873fe57feb76f1ee7632d1)

![{\displaystyle G_{1}[m_{3},n_{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/c5169569e417019b3ab4c0aeb5bf2a384aa68307)

![{\displaystyle F[((m_{1}P_{1}+m_{2}P_{2}))_{N}]=\sum _{n_{2}=0}^{P_{1}-1}G_{1}[m_{3},n_{2}]e^{-i{\frac {2\pi }{P_{1}}}m_{2}P_{2}n_{2}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/b1d6ab6f9dd4affdce3d9499aedd1d1082616a7e)

![{\displaystyle G_{2}[m_{3},m_{4}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/0232af78b3229760d65e779679576263ca9d48ee)

![{\displaystyle F[m]=F[((m_{1}P_{1}+m_{2}P_{2}))_{N}]=G_{2}[m_{3},m_{4}]=G_{2}[((m_{1}P_{1}))_{P_{2}},((m_{2}P_{2}))_{P_{1}}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/062237ab486830ce263acd942e5e4d6496e428c5)